در بخش ۲ توضیحات کلی در رابطه با IC گیت درایو HCPL-316J بیان گردید. در این قسمت به توضیح عملکرد آن میپردازیم.

استفاده یا عملکرد معمول – معرفی عملی تشخیص خطا و حفاظت

سطح توان یک اینورتر سه فاز معمولی حساس به چند نوع خرابی است، که بیشتر آنها خرابی IGBT ها هستند. این حالت های خرابی را می توان به چهار دسته اساسی تقسیم کرد: مدارهای اتصال کوتاه فاز یا ریل منبع تغذیه به علت قطعی اتصال توسط کاربر یا سیم کشی بد، عدم کنترل سیگنال های کنترل به علت نویز، خطاهای محاسباتی و اضافه بار ناشی از بار و خرابی های اجزا در مدار های درایو گیت.

تحت هر یک از این شرایط خطا، جریانIGBTها می تواند به سرعت افزایش پیدا کند و باعث افزایش بیش از حد توان و ایجاد حرارت شود. IGBT ها هنگامی که جریان بار به جریان اشباع دستگاه نزدیک می شود آسیب می بینند و ولتاژ کلکتور به امیتر بیشتر از سطح ولتاژ اشباع می شود. این از تلفات توان به سرعت کلید را بیش از حد گرم می کند و آن را از بین می برد. برای جلوگیری از آسیب به درایو، حفاظت از خطا باید به منظور کاهش یا خاموش کردن اضافه جریانها در حین حالت خطا انجام شود.

شرح عملکرد/ زمان بندی

شکل ۶۳ زیر شکل موج ورودی و خروجی را در شرایط عملیات عادی، حالت خطای desat و رفتار reset نرمال نشان می دهد.

– عملکرد عادی

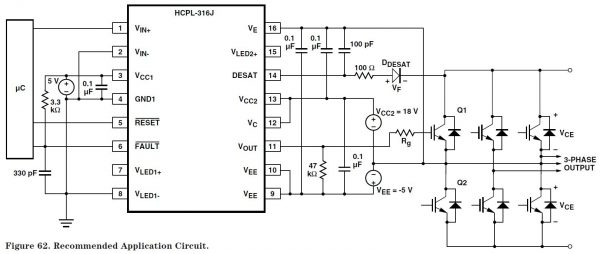

در حین عملکرد عادی، VOUT آی سی HCPL-316J توسط VIN+ یا VIN- کنترل میشود که به وسیله ولتاژ کلکتور به امیتر IGBT که از طریق DDESAT نظارت می شود. خروجی FAULT، به صورت high است و ورودی RESET باید high باشد. به شکل ۶۳ نگاه کنید.

– وضعیت خطا

هنگامی که ولتاژ در پین DESAT بیش از ۷ ولت و در حالی که IGBT روشن است، شود، VOUT به آرامی کاهش می یابد تا IGBT به صورت “soft” خاموش شود و از ولتاژ القایی بزرگ ناشی از d/dt، جلوگیری شود. همچنین activated یک کانال فیدبک داخلی است که خروجی FAULT را low می کند تا به میکروکنترلر وضعیت خطا را اطلاع رسانی کند. به شکل ۶۳ نگاه کنید.

– Reset

خروجی FAULT تا زمانی که RESET به صورت low می شود، low باقی می ماند. شکل ۶۳ را ببینید. در مدت زمانی که پین RESET به صورت low است، پین های ورودی باید برای حالت low خروجی (VIN+ به صورت LOW یا VIN- به صورت HIGH) آماده شوند. این ممکن است با کنترل نرم افزار (به عنوان مثال از میکروکنترلر) و یا کنترل سخت افزار انجام شود.

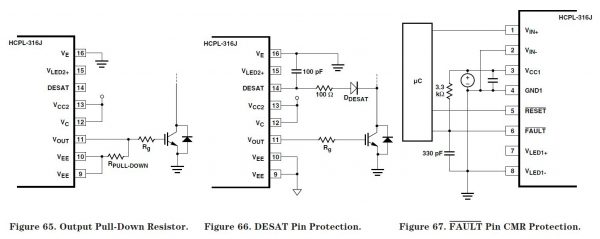

discharge آرام گیتIGBT درهنگام شرایط خطا

هنگامی که یک خطای desaturation تشخیص داده می شود، یک دستگاه ضعیف pull-down در قسمت خروجی HCPL-316J روشن خواهد شد تا IGBT به صورت soft خاموش شود. این دستگاه به آرامی ‘گیت IGBT را discharge می کند تا از تغییرات سریع در جریان drain جلوگیری کند که می تواند موجب خسارات ناشی از وارد شدن ولتاژ ضربه به دلیل سلف پارازیت سیم ها یا پایه ها شود. در خلال خاموش کردن آرام، خروجی بزرگ pull-down دستگاه به صورت خاموش باقی می ماند تا ولتاژ خروجی پایین تر از VEE+2 ولت باشد، در این زمان دستگاه pull down بزرگ، گیت IGBT را به VEE متصل می کند.

زمان خالی(بیکار) تشخیص خطا DESAT

مدار تشخیص خطا DESAT باید برای یک دوره زمانی کوتاه پس از روشن شدن IGBT غیر فعال شود تا ولتاژ کلکتور به کمتر از theshold ولتاژ DESAT کاهش یابد. این دوره زمانی که زمان خالی DESAT (DESAT blanking time) نامیده می شود، توسط جریان شارژ DESAT، آستانه یا threshold ولتاژ DESAT و خازن خارجی DESAT کنترل می شود. زمان خالی اسمی بر حسب ظرفیت خارجی (CBLANK)، ولتاژ آستانه FAULT یا (VDESAT) و جریان شارژ (ICHG) به صورت tBLANK = CBLANK * VDESAT/ICHG محاسبه می شود. زمان خالی اسمی با خازن با ظرفیت ۱۰۰ پیکوفاراد توصیه شده، ۱۰۰ pF * 7 V / 250 uA=2.8 usec است. مقدار خازنی می تواند تا حدی کمی برای تنظیم زمان خالی درجه بندی شود، هر چند مقدار کمتر از ۱۰۰ پیکوفاراد توصیه نمی شود. این زمان خالی اسمی نیز نشان دهنده طولانی ترین زمان برای HCPL-316J برای پاسخ گویی به شرایط خطای DESAT است. اگر IGBT روشن باشد در حالی که کلکتور و امیتر به سطح های تغذیه اتصال کوتاه شده اند (تغییر در کوتاه مدت)، پس از حدود ۳ μs، روند خاموش شدن soft شروع می شود. اگر پس از اینکه IGBT روشن شده است، امیتر و کلکتور به سطوح ولتاژ تغذیه وصل شوند، زمان پاسخ بسیار سریعتر خواهد بود به دلیل خازن موازی پارازیتی دیود DESAT. توصیه می شود خازن ۱۰۰ پیکوفاراد باید زمان خالی کافی را فراهم کند تا دفعات(زمان) پاسخ خطا را برای اکثر کاربردها فراهم کند.

Lockout کاهش ولتاژ

ویژگی Lockout کاهش ولتاژ HCPL-316J یا (UVLO) برای جلوگیری از استفاده در ولتاژ ناکافی گیت به IGBT است که به وسیله low شدن خروجی در حین روشن شدن آیسی انجام می شود، طراحی شده است. IGBT ها به طور معمول نیاز به ولتاژ گیت ۱۵ ولت دارند تا ولتاژ VCE (ON) نامی خود را به دست آورند. معمولا در ولتاژ های گیت زیر ۱۳ ولت، ولتاژ روی آنها (on-voltage) به طور چشمگیری افزایش می یابد، به خصوص در جریان های بالاتر. در ولتاژ گیت بسیار کم (زیر ۱۰ ولت)، IGBT ممکن است در محدوده خطی عمل کند و به سرعت و بیش از حد گرم شود. ویژگی UVLO موجب می شود تا هر زمانی که تغذیه عملکرد (VCC2) به صورت ناکافی اعمال می شود، خروجی clamp شود. هنگامی که VCC2بیش از VUVLO+ (threshold مثبت UVLO)، clamp وارد بر UVLO آزاد می شود تا خروجی دستگاه در پاسخ به سیگنال های ورودی فعال شود. همانطور که VCC2 از ۰ ولت افزایش می یابد، (در برخی از سطوح زیر VUVLO+) ابتدا مدار حفاظت DESAT فعال می شود. همانطور که VCC2 بیشتر (بالاتر از VUVLO+) افزایش می یابد، clamp روی UVLO برداشته می شود. قبل از آنکه Clamp روی UVLO برداشته شود، محافظت DESAT فعال بوده است. بنابراین، ویژگی های تشخیص خطای UVLO و DESAT با هم کار می کنند تا بدون در نظر گرفتن ولتاژ منبع (VCC2) حفاظت بدون اشتباهی را ارائه دهند.

توصیف مدار شماتیک

رفتار عملکرد HCPL-316J توسط نمودار منطقی در شکل ۶۴ نشان داده شده است که به طور کامل تعامل و sequence سیگنال های داخلی و خارجی در HCPL-316J را توصیف می کند.

IC ورودی

در حالت سوئیچینگ عادی، هیچ خطای خروجی شناسایی نمی شود و وضعیت low درlatch خطا باعث می شود سیگنال های ورودی LED، سیگنال را کنترل کنند. خروجی خطا در حالت open-collector است و وضعیت پین Reset بر کنترل گیت IGBT تاثیر نمی گذارد. هنگامی که یک خطا شناسایی می شود، خروجی FAULT و ورودی سیگنال هر دو latch می شوند. خروجی خطا به وضعیت active low تغییر می کند و سیگنال LED خاموش می شود (خروجی LOW). وضعیت latch تا زمانی که پین Reset به صورت pull low شود، ادامه خواهد داشت.

خروجی IC

سه سیگنال داخلی وضعیت خروجی درایور را کنترل می کنند: حالت سیگنال LED و سیگنال های UVLO و Fault. اگر هیچ خطایی در کلکتور IGBT شناسایی نشود و ولتاژ منبع تغذیه بالاتر از threshold یا آستانه UVLO باشد، سیگنال LED حالت خروجی درایور را کنترل می کند. منطق درایورشامل یک interlock برای اطمینان از اینکه دستگاه های pull-up و pull-down در قسمت خروجی هرگز در یک زمان یکسان {فعال} نیستند. اگر وضعیت کاهش ولتاژ یا undervoltage تشخیص داده شود، خروجی به صورت فعالانه با استفاده از دستگاه DMX 50x، بدون در نظر گرفتن وضعیت LED، به صورت low می شود. اگر یک خطای اشباع شدن IGBT در حالی که LED سیگنال روشن است شناسایی شود، سیگنال خطا در وضعیت high قرار می گیرد. دارلینگتون سه گانه یا triple darlington و دستگاه ۵۰X DMOS غیرفعال می شوند و یک دستگاه کوچکتر pull-down شده DMOS کوچکتر به منظور دشارژ شدن آرام گیت IGBT فعال می شود. هنگامی که خروجی زیر دو ولت پایین می آید، دستگاه ۵۰x DMOS دوباره روشن می شود، گیت IGBT را به Vee وصل یا clamp می کند. سیگنال خطا در حالت high باقی می ماند تا زمانی که سیگنال LED خاموش شود.

ادامه دارد…

منبع:گروه الکترونیک قدرت دانشگاه تهران