در بخش ۴ نحوه عملکرد IC گیت درایو HCPL-316J بیان گردید. در این بخش به بیان محاسبات و ملاحظات لازم در استفاده از این محصول میپردازیم.

توان/ طرح ملاحظات عملکرد در حداکثر توان مجاز(تنظیم مقدار RG):

هنگام انتخاب مقدار RG، مهم است که تأیید کنیم که تلفات توان HCPL-316J در حداکثر توان مجاز چقدر است. مراحل انجام این کار عبارتند از:

۱٫ حداقل RG مورد نظر را محاسبه کنید.

۲٫ محاسبه کل توان تلف شده در قسمت اشاره شده در شکل ۷۷ (متوسط انرژی سوئیچینگ عرضه شده به HCPL-316J در هر سیکل در مقابل طرح RG)

۳٫ مقادیر ورودی و خروجی تلفات توان محاسبه شده در مرحله ۲ را مقایسه کنید تا حداکثر میزان توصیه شده برای HCPL-316J محاسبه شود.(اگر حداکثر سطح توصیه شده بیش از حد باشد، ممکن است لازم باشد مقدار RG را برای کاهش توان سوئیچینگ افزایش دهیم و مرحله ۲ را تکرار کنیم.)

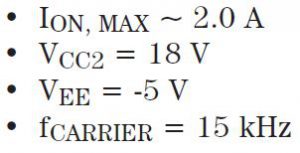

به عنوان مثال، کل توان تلف شده ورودی و خروجی را می توان با توجه به شرایط زیر محاسبه کرد:

مرحله ۱: محاسبه حداقل RG از مشخصات پیک IOL:

برای پیدا کردن حداکثر شارژ IOL فرض کنید که گیت در ابتدا تا مقدار پایدار VEE شارژ شده باشد. بنابراین رابطه زیر را اعمال کنید:

(طبق شکل ۷۶ توجه داشته باشید که مقدار واقعی IOL ممکن است از مقدار محاسبه شده از مدل ساده نمایش داده شده متفاوت باشد.)

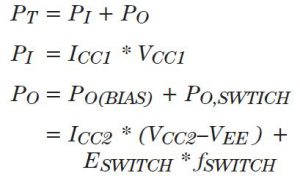

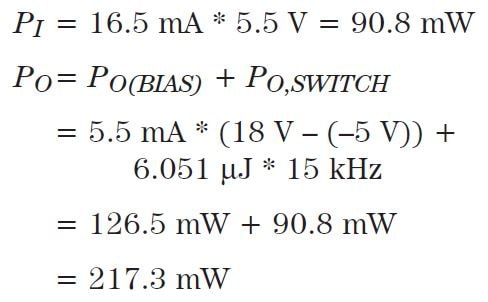

مرحله ۲: محاسبه کل تلفات توان HCPL-316J:

کل تلفات توان (HCPL-316J(PT برابر با مقدار توان سمت ورودی (PI) و توان سمت خروجی (PO) است:

توضیحات:

(Po(bias: تلفات توان پایدار در HCPL-316J به علت biasing دستگاه است.

(Po(switch: تلفات توان پایدار در HCPL-316J به علت شارژ و دشارژ توان گیت دستگاه است.

(E(switch: میانگین انرژی تلف شده در HCPL-316J به علت سوئیچینگ در توان دستگاه در یک سیکل سوئیچ زنی است. .(μJ / cycle)

(f(switch: میانگین فرکانس سیگنال حامل.

برای RG = 10.5، مقدار خوانده شده از شکل ۷۷ برابر ESWITCH = 6.05 μJ است. فرض کنید میانگین بدترین مورد ICC1 = 16.5 میلی آمپر (که توسط میانگین ICC1H و ICC1L داده می شود) باشد. به طور مشابه متوسط ICC2 = 5.5 میلی آمپر است.

مرحله ۳: مقایسه توان تلف شده محاسبه شده با اندازه حداکثر مقادیر HCPL-316J:

برای مثال:

بنابراین، برای مثال، از حداکثر اندازه مطلوب برای تلفات توان فراتر نرفته ایم. لطفا به بخش Thermal Model زیر مراجعه کنید تا توضیحی در مورد چگونگی محاسبه حداکثر دما اتصال HCPL-316J را برای یک پیکربندی یک طرح برد PC را مشاهده کنید.

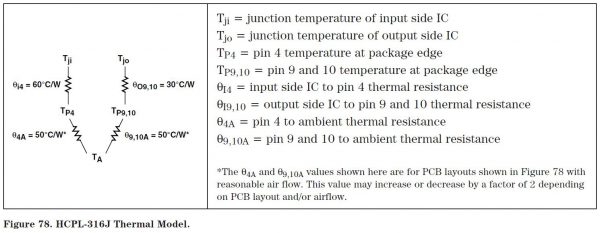

مدل حرارتی

HCPL-316J طراحی شده است تا بیشتر حرارت را از طریق پین ۴ برای ورودی IC و پین ۹ و ۱۰ برای خروجی IC از بین ببرد و پراکنده کند. (برای این منظور دو پین VEE در سمت خروجی وجود دارد، پین های ۹ و ۱۰). جریان گرما از طریق پین های دیگر یا از طریق package به طور مستقیم به محیط ناچیز محسوب می شود و در اینجا مدل سازی نمی شود.

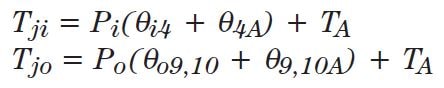

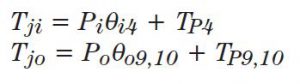

برای رسیدن به تلفات توان مشخص شده در مشخصات حداکثر، ضروری است که پینهای ۴، ۹ و ۱۰، ground plane هایی داشته باشند که به آنها متصل شده است. تا زمانی که مشخصات حداکثر توان را نادیده گرفته نشود، تنها محدودیت دیگر مقدار قدرت که می تواند از بین برود، اندازه حداکثر درجه دمای محل اتصال که ۱۲۵ درجه سانتیگراد است، می باشد. دمای اتصال می تواند با معادلات زیر محاسبه شود:

به صورتی که:

Pi: توان ورودی IC

Po: توان خروجی IC

از آنجا که θ_۴A وθ_۹,۱۰A به شکل PCB و جریان هوا بستگی دارند، تعداد دقیق آنها ممکن است در دسترس نباشد. بنابراین، یک روش دقیق تر محاسبه دمای اتصال به کمک معادلات زیر است:

این معادلات، با این حال، نیاز دارد که دمای پین های ۴، ۹ و ۱۰ با یک couple حرارتی بر روی پین در لبه پکیج HCPL-316J اندازه گیری شود.

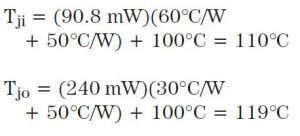

از مثال محاسبه تلفات توان قبلی:

Pi = 90.8 mW, Po = 314 mW, TA =100°C و فرض بر مدل حرارتی نشان داده شده در شکل ۷۷ زیر می باشد.

هر کدام از آنها در مشخصات حداکثر ۱۲۵ درجه سانتی گراد هستند.

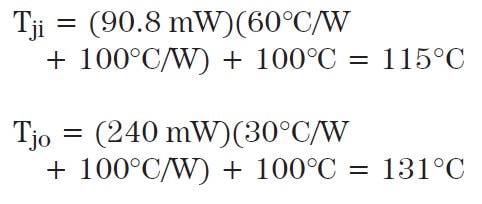

با این حال، اگر ما فرض بدترین حالت طرح PCB را کنیم و جریان هوا را در نظر نگیریم که در آن برآورد θ_۴A و θ_۹,۱۰A را ۱۰۰ درجه سانتی گراد بر وات است، سپس درجه حرارت اتصال به صورت زیر می شود:

دمای اتصال IC خروجی بیش از حداکثر مطلق مشخصات که ۱۲۵ درجه سانتیگراد است، تجاوز کرده است. در این مورد، طرح PCB و جریان هوا باید طوری طراحی شوند تا دمای اتصال IC خروجی از ۱۲۵ درجه سانتیگراد فراتر نرود.

اگر درجه حرارت اتصال محاسبه شده برای مدل حرارتی در شکل ۷۸ بالاتر از ۱۲۵ درجه سانتیگراد باشد، دمای پین های ۹ و ۱۰ (در لبه پگیج) در بدترین شرایط عملکرد برای تخمین دمای پیوند باید اندازه گیری شوند.

ملاحظات طرح برد مدار چاپی

همیشه باید فاصله مناسب بین مدارهای ایزوله شده با ولتاژ بالا و هر مدار ورودی رفرنس داده شده (input referenced circuitry) حفظ شود. باید مراقب باشید که حداقل فاصله بین دو ناحیه جدا شده از سمت نزدیک بالای صفحه مدار چاپی فراهم شود. فاصله ناکافی ایزولاسیون موثر را کاهش می دهد و coupling پارازیتی را افزایش می دهد که عملکرد CMR را کاهش می دهد.

قرار دادن و مسیریابی یا routing خازن های bypass تغذیه توجه زیادی را نیاز دارد. در حالت های گذرا سوئیچینگ، عمده بار شارژ گیت توسط خازن های bypass تامین می شود. کوتاه نگه داشتن طول ترک خازن bypass موجب کاهش ripple شکل موج خروجی و شکل موج سوئیچینگ تمیز (clean) خواهد شد.

اتصالات صفحه (HCP-316J(Plane connections به پین ۴ (GND1) و پین ۹ و ۱۰ (VEE) برای رسیدن به حداکثر تلفات توان ضروری است تا بیشترگرما تولید شده از طریق این پین ها را از بین ببرد. تلفات توان واقعی به محیط مورد استفاده (طرح PCB، جریان هوا، جایگذاری بخش ها و غیره) بستگی دارد. برای جزئیات بیشتر در مورد چگونگی تخمین دمای اتصال، بخش مدل حرارتی را ببینید.

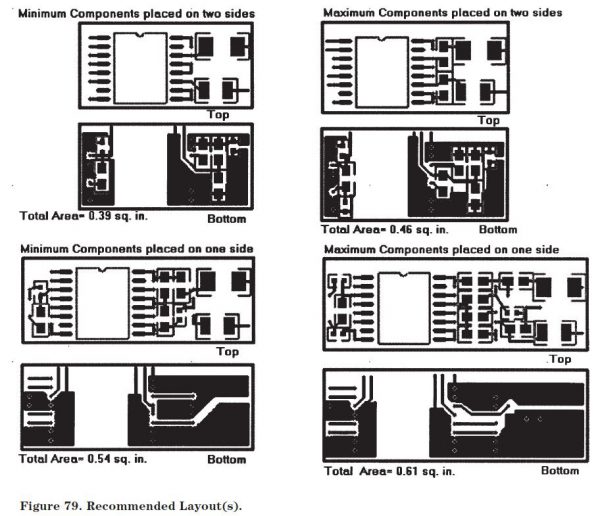

نمونه های طراحی های زیر دارای ضریب اطمینان و ویژگی های حرارتی هستند، footprint های کوچک PCB را نشان می دهند و به راحتی سیگنال و خطوط تغذیه را متصل می کنند. چهار نمونه شامل قرار گیری اجزای یک طرفه و دو طرفه و همچنین مدارهای minimal و بهبود یافته عملکرد می باشند.

ملاحظات (Propagation Delay Difference (PDD سیستم

HCPL-316J شامل یک ویژگی (Propagation Delay Difference (PDD است که به منظور کمک به طراحان قرار داده شده است و برای حداقل کردن “زمان مرده” یا “dead time” در طراحی های اینورتر های توان آنهاست. dead time زمانی است که طی آن هر دو ترانزیستور قدرت بالا و پایین (Q1 و Q2 در شکل ۶۲) خاموش می شوند. هرگونه همپوشانی در هدایت Q1 و Q2 موجب جریانهای بزرگی می شود که از طریق دستگاه های قدرت بین سطح های ولتاژ بالا و پایین جریان می یابند و شرایطی را ممکن است ایجاد کند که می تواند فاجعه آمیز باشد و باید از آن جلوگیری شود.

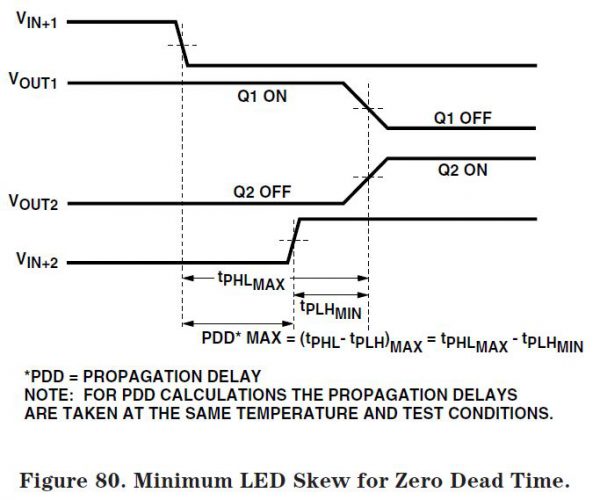

برای حداقل کردن dead time در یک طراحی، روشن شدن HCPL-316J درایو کننده Q2 باید تاخیر داشته باشد. (وابسته به خاموش شدن HCPL-316J درایو کننده Q1). بنابراین همان طور که در شکل ۸۰ نمایش داده شده است، در بدترین شرایط، ترانزیستور Q1 تازه خاموش شده است، موقعی که Q2 روشن می شود. مقدار تاخیر مورد نیاز برای رسیدن به این شرایط مساوی با حداکثر مقدار مشخصات اختلاف تاخیر پارازیتی است.((PDD(max). که تعیین شده است که در محدوده دمایی -۴۰ تا ۱۰۰ درجه سانتی گراد، برابر با ۴۰۰ نانوثانیه باشد.

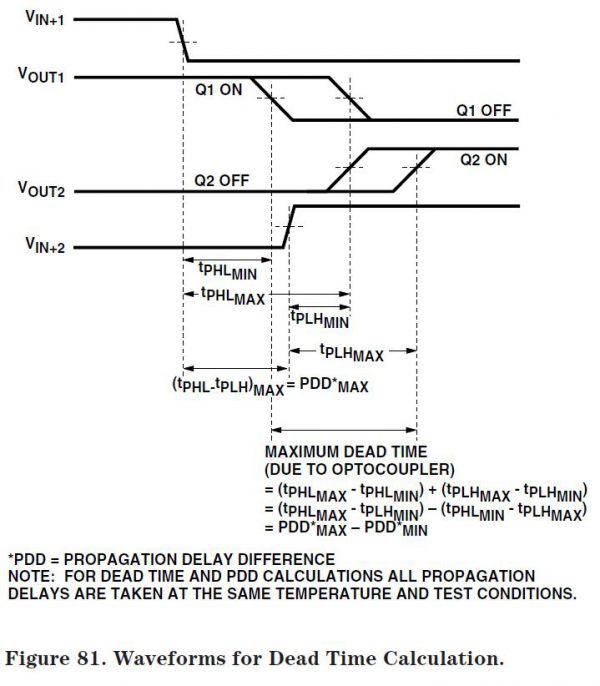

تاخیر سیگنال های روشن شدن HCPL-316J به وسیله حداکثر اختلاف تاخیر پارازیتی، تضمین می کند که حداقل dead time صفر است، اما به طراح اجازه نمی دهد که حداکثر dead time چقدر است. حداکثر dead time معادل اختلاف بین حداکثر و حداقل مشخصات تاخیر پارازیتی است، همانطور که در شکل ۸۱ نشان داده شده است. حداکثر dead time برای HCPL-316J 800، برابر ۴۰۰ns نانوثانیه در طول عملیات محدوده دما -۴۰ ° C تا ۱۰۰ ° C است.

توجه داشته باشید که تاخیرهای پارازیتی مورد استفاده برای محاسبه PDD و dead time در دماهای برابر و شرایط آزمایشی گرفته می شود، زیرا اپتوکوپلرهای مورد نظر معمولا در مجاورت یکدیگر قرار می گیرند و IGBT های یکسان را تعویض می کنند.

پایان