انتخاب توپولوژی

توپولوژی Flyback بهطور گستردهای در اکثر درایوهای متغیر سرعت مورد استفاده قرار میگیرد. این ساختار در توان نامی کمتر از ۱۵۰ وات مورد استفاده قرار میگیرد و ایزولاسیون را برقرار میکند؛ تنها از یک عنصر مغناطیسی بهره میبرد و فضای کمتری را اشغال میکند. ویژگی جذاب استفاده از این توپولوژی این است که هیچ کلید خروجی مورد نیاز نیست. مزایای دیگر عبارتاند از ایجاد آسان ولتاژ خروجی چندگانه، تعداد جزء بسیار کم و هزینه کم.

مبدلهای فلایبک با استفاده از یک کلید، تمام ولتاژ که تقریباً ۱۵۰۰ ولت محاسبه میشود بر روی کلید میافتد پسنیاز به یک ماسفت با رنج ولتاژ بالا و گرانقیمت هستیم. این موضوع در ولتاژهای ۶۹۰ ولت ورودی حادتر میشود.

در مورد مبدل فلایبک Cascade (شکل بالا سمت راست)، ماسفت Q1 با گیت شارژ کم Qg، به ماسفت سری Q2 متصل میشود. در این مورد، Q1 بهطور مستقیم از کنترلکننده PWM درایو میشود. با پیکربندی Cascade، توزیع ولتاژ روی دو کلید ممکن میشود، در نتیجه یک رنج کلی ولتاژ برابر با مجموع ولتاژ ماسفتها است. با استفاده از روش Cascade با دو ماسفت ۹۰۰ ولت کمهزینه، یک ولتاژ کلی ۱۸۰۰ ولت به دست میآید، که باعث میشود عملکرد منبع تغذیه در ولتاژ ورودی مطلوب ۳۵۰ تا ۷۲۰ ولت مجاز باشد. این مدار ساده نیاز به یک مدار محدود کننده دارد، که از TVS بر روی منبع ورودی حاصل میشود.

بررسی حالت روشنشدن کلیدها

هنگامی که ولتاژ گیت سورس (Vgs1) ماسفت Q1 بیشتر از ولتاژ آستانه گیت آن باشد، Q1 روشن میشود. بهمحض اینکه Q1 روشن میشود، سورس Q2 از طریق Q1 به زمین متصل میشود، که باعث میشود ولتاژ zener بر روی گیت سورس Q2 قرار گیرد و باعث روشن شدن ماسفت Q2 میشود. سپس، مبدل Cascade به حالت هدایت میرود؛ در نتیجه جریان از طریق سیمپیچ اولیه ترانسفورماتور فلایبک و دو سوئیچ (Q1 و Q2) برقرار میشود. افت ولتاژ در هر دو ماسفت برابر با ولتاژ آنها در حالت روشنشدن است.

بررسی حالت خاموششدن کلیدها

هنگامی که ولتاژ گیت-سورس Vgs1 کمتر از ولتاژ آستانه گیت Vth1 است، ماسفت Q1 خاموش میشود. جریان از طریق خازن بین درین-سورس ماسفت Q1 برقرار میشود؛ بنابراین ولتاژ Vds1 بر روی Q1 شروع به افزایش میکند. در این زمان ولتاژ پایانه درین ماسفت Q2 شروع به افزایش میکند، پس ولتاژ Vgs2 یعنی ولتاژ گیت-سورس ماسفت کاهش مییابد. وقتی ولتاژ گیت-سورس Q2 به ولتاژ آستانه گیت Vth2 برسد، Q2 خاموش میشود.

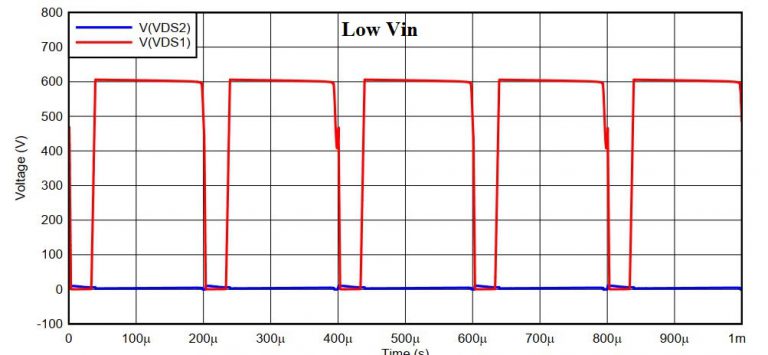

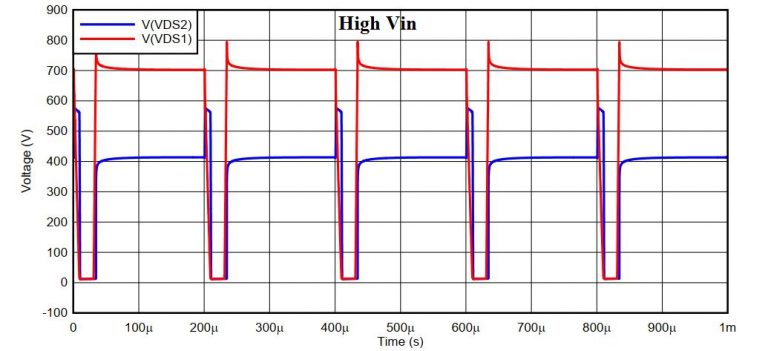

در شکل زیر مقایسه ولتاژ درین-سورس دو ماسفت سری در دو حالت ولتاژ پایین و ولتاژ بالا انجام شده است. همانطور که از شکل مشخص است، در ولتاژ پایین تمام ولتاژ بر روی درین-سورس ماسفت پایین میافتد، در حالی که در ولتاژ بالا مقداری از ولتاژ بر روی ماسفت بالا و مقداری بر روی ماسفت پایین خواهد افتاد؛ پس نسبت تقسیم ولتاژ مساوی نیست.

در حالت ولتاژ ورودی بالا نیز تقسیم ولتاژ بر روی دو ماسفت مطابق شکل زیر است.

منبع: گروه الکترونیک قدرت دانشگاه تهران