وقتی صحبت از معماری کامپیوتر به میان میآید، معماری x86 یا ARM در ذهنمان تداعی میشود. آیا درباره معماری Open source نوظهور که روزبهروز محبوبتر میشود، یعنی RISC-V (یا همانطور که خوانده میشود Risc-Five) شنیدهاید؟ اگر پاسختان خیر است، حتما باید دامنه اطلاعات خود را در این باره بیشتر کنید! زیرا در آینده نزدیک شاهد استفاده گسترده از این تکنولوژی خواهیم بود.

باماهمراه باشید.

ISA چیست؟

پیش از ادامه صحبت درباره RISC-V بد نیست معرفی مختصری از ISA داشته باشیم. ISA یا معماری مجموعه دستورات کامپیوتر، یک مدل انتزاعی از معماری یک کامپیوتر است که جزییاتی مثل مدل رجیسترها، دستورات ماشین و … را مشخص میکند. مثالی از محقق سازی این طرح انتزاعی ساخت یک واحد پردازنده مرکزی (CPU) است، به این عمل پیادهسازی گفته میشود. ISA هایی که در حال حاضر بهطور گسترده استفاده میشوند x86 (از شرکت Intel) و ARM هستند. از معماریهای قدیمیتر نیز میتوان SPARC و VAX و از ریزپردازندههای اولیه میتوان Z80 و 6502 را نام برد.

نکتهای درباره ISA ها که معمولاً به آن توجه نمیشود این است که ISA ها داراییهای فکری هستند که توسط سازنده آنها به ثبت رسیده است و حقوق آنها محفوظ است. این یعنی اگر یک تولیدکننده مثل Freescale یا Broadcom بخواهد در طرح خود از یک پردازنده منطبق بر ARM استفاده کند، باید از شرکت ARM (مالک این معماری)، مجوز دریافت کند.

شما میتوانید معماری موردنظر و مختص خودتان را طراحی و استفاده کنید اما باید در نظر داشته باشید که کار سادهای نخواهد بود. طراحی یک ISA شامل مشخص کردن ریزترین جزییات یک سیستم پردازشی است. بهعنوانمثال معماری x86، برای اولین بار در سال 1978 و در چیپ 8086 ساخت شرکت Intel استفاده شد. شروع کار معماری Arm نیز سال 1981 در کامپیوتر BBC Micro، ساخته شرکت Acorn بود. هردوی این معماریها از آن زمان درحالتوسعه و گسترش بودهاند.

RISC-V چیست؟

RISC-V یک ISA طراحیشده بر اساس قواعد “کامپیوتر با مجموعه دستورات کاهشیافته” یا RISC است. نکته مهم درباره این معماری این است که برخلاف بیشتر معماریهای موجود، RISC-V بهصورت Open-source به ثبت رسیده است و برای استفاده از آن نیاز به پرداخت هیچ هزینهای نیست! به همین دلیل چون شرکتهای تولیدکننده میکروکنترلر و soc برای پردازنده نیاز به پرداخت لایسنس ندارد انتظار میرود که هزینه تمامشده چیپ ها کمتر از نمونه مشابه arm باشد.

تاریخچه RISC-V

این پروژه در سال 2010 و در دانشگاه برکلی کالیفرنیا به همراه جمعی از مشارکتکنندگان داوطلب دیگر بهعنوان زیرمجموعهای از پروژه آزمایشگاه پردازش موازی (Par Lab) شروع شد. پروژه Par Lab در جهت پیشرفت پردازش موازی، در سال 2008 شکل گرفت و شرکتهای مهمی ازجمله Intel و Microsoft با سرمایه 10 میلیون دلاری از این پروژه پشتیبانی کردند و در سال 2013 پایان یافت. پسازآن، پروژه Par Lab از پشتیبانیهای مالی دیگری برخوردار شد، اما بودجه آنها صرف توسعه معماری RISC-V نمیشد.

نکته قابلتوجه این بود که همه پروژههای Par Lab (ازجمله RISC-V و Chisel) بهصورت Open source و تحت لیسانس BSD (Berkeley Software Distribution) به ثبت رسیدند.بعد از انتشار طرحهای اولیهی RISC-V، اولین چیپ بر اساس این معماری در سال 2011 با تکنولوژی 28nm FDSOI و با حمایت شرکت ST Microelectronics تولید شد. بعدازآن در سال 2014 مقالهای در رابطه با مزایای معماری Open source منتشر گردید.

در سال 2015 اولین کارگاه RISC-V برگزار شد و کمی بعد بهمنظور پایدار کردن پروژه و همچنین ایجاد جذابیت برای استفادهکنندههای تجاری، یک موسسه رسمی RISC-V برای مالکیت، پشتیبانی و انتشار این معماری تشکیل شد. این موسسه که اخیراً به RISC-V International تغییر نام داده، در کشور سوییس مستقرشده است.

دلیل اهمیت RISC-V

ازنظر فنی، RISC-V ویژگی خلاقانه جدیدی ندارد. این معماری از اصول ثابت RISC پیروی کرده و از یک معماری load-store بهره میگیرد. مزیت این امر، سازگاری با معماری شناختهشده است.

RISC-V مثل معماریهای دیگر، جزییات کامل مربوط به سطوح مختلف مجموعه دستورات را شرح میدهد. این جزییات شامل مواردی مثل دستورات نوع 32 و 64 بیتی و همچنین امکان گسترش و پشتیبانی از دستورات floating point میشود. همین امر موجب میشود که امکان تنوع در طراحی سختافزار برای کاربردهای مختلف به وجود آید. از میکروکنترلرهای کوچک گرفته تا کامپیوترهای شخصی و حتی ابرکامپیوترهای دارای vector processor.

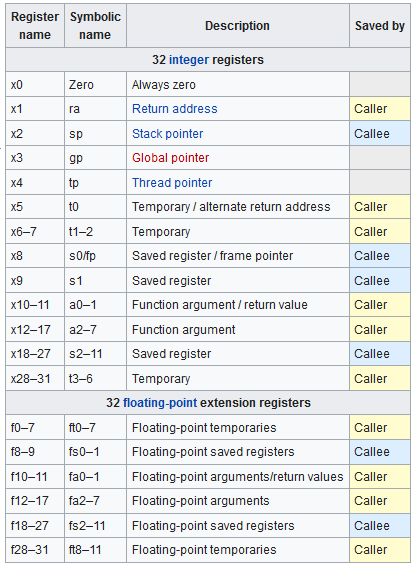

رجیسترها در RISC-V

در این معماری 32 (یا 16 رجیستر) رجیستر integer دارد. در حالتی که ماژول نیز پیادهسازی شده باشد، 32 رجیستر floating-point را هم شامل میشود. علاوهبر اینها رجیسترهای دستورات دسترسی به حافظه و آدرس دستورات نیز وجود دارند. رجیسترهای status و کنترلی نیز وجود دارند اما برنامهها در حالت user-mode تنها به رجیسترهای عمومی و مدیریت floating-point دسترسی دارند. قابلذکر است که دستوری برای ذخیره و بازیابی چند رجیستر تعبیه نشده است. دلیل این امر احتمالاً عدم نیاز، پیچیدگی زیاد یا شاید سرعت کم چنین دستوری در نظر گرفتهشده است.

جدول مربوط به رجیسترهای integer و floating-point در شکل زیر دیده میشود:

دسترسی به حافظه

همانطور که گفته شد، RISC-V مثل بسیاری از معماریهای دیگری که بر پایه RISC هستند، یک معماری load-store است. یعنی اینکه رجیسترهای instruction address only، عمل خواندن دستورات در حافظه و یا ذخیره آنها در حافظه را انجام میدهند. اکثر دستورات load و store شامل یک آفست 12 بیتی و دو میدان مشخصکننده رجیستر هستند. یک رجیستر base register و رجیستر دیگر، رجیستر منبع (برای عملیات store) و رجیستر مقصد (برای عملیات load) است. برای پیدا کردن آدرس، آفست 12 بیتی به مقدار base register اضافه میشود.

حافظه در RISC-V با بایتهای آن آدرسدهی میشود و ترتیب دستورات نیز little-endian در نظر گرفتهشده است. ترتیب بایتهای دادهها نیز توسط Interface محیط اجرای کد تعریف میشود. طراحی RISC-V از ابتدا برای کاهش پیچیدگی و هزینه و همچنین انطباق با طرحهای شناختهشده (مثل x86) بهصورت little endian بوده است. بااینحال نمونههای Big-endian و bi-endian نیز تعریفشدهاند.

پشتیبانی نرمافزاری

یک مشکل معمول که معماریهای نوظهور به آن دچار میشوند، کمبود طراحیهای CPU و همچنین پشتیبانی نرمافزاری است. در حال حاضر تعداد بسیار زیادی طرح CPU برای RISC-V وجود دارد. ازنظر نرمافزاری نیز RISC-V توسط تعدادی از کامپایلرها ازجمله GCC، پشتیبانی میشود. علاوه بر آن ابزار LLVM، شبیهسازهای OVPSim و SPike و همچنین یک شبیهساز در QEMU برای این معماری وجود دارند. معماری RISC-V از سیستم عامل های کرنل لینوکس، FreeBSD، NetBSD و همچنین OpenBSD پشتیبانی میکند.

پشتیبانی سختافزاری

شرکتهایی که سختافزار RISC-V تولید میکنند یا چنین محصولی را اعلام کردهاند شامل Qualcomm ،Samsung ،Alibaba و حتی Nvidia میشوند. استارتآّپهایی مثل SiFive نیز هستند که در تلاشاند پردازندههایی بر اساس این معماری، برای رقابت با پردازندههای Arm تولید کنند. طیف این سختافزارها از میکروکنترلرها تا SOM و SOC های باقابلیت اجرای لینوکس و حتی FPGA های دارای هسته RISC-V را شامل میشود.

برخی محصولات قابل توجه که از RISC-V استفاده میکنند:

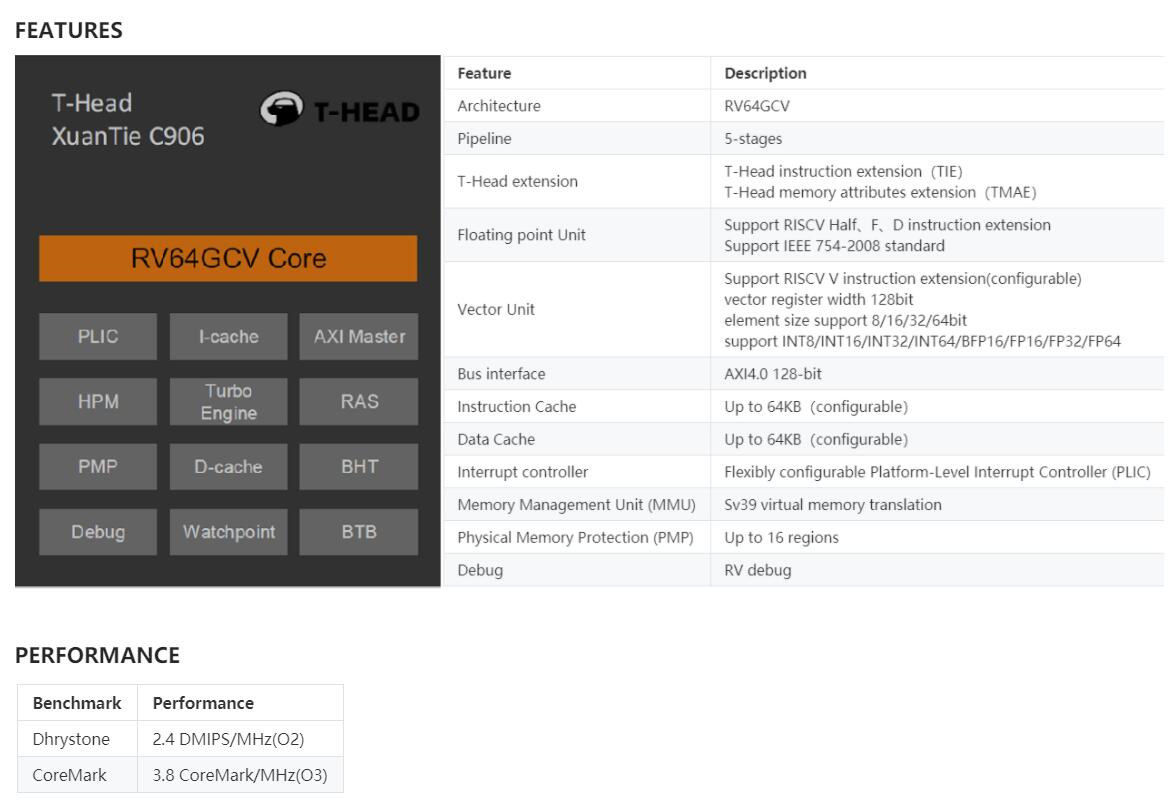

- پردازنده XuanTie C906 ساخته شرکت Allwinner Technology

- پردازنده کمکی RISC-V که شرکت Espressif به میکروکنترلر ESP32-S2 خود اضافه کرده است. برخی مشخصات میکروکنترلر ESP32-C3 که براساس RISC-V طراحی شده :

- پردازنده تک هستهای 32 بیتی

- میکروکنترلر بر پایه RISC-V با 400KB حافظه SRAM

- فرکانس کاری 160MHz

- میکروچیپ Mi-V ecosystem که شامل CPU های soft-core RISC-V میشود.

- Seeed Studio Perf-V بر پایه یک Xilinx Artix-7 RISC-V FPGA

- BeagleV که یک کامپیوتر تک بوردی ارزان قیمت با قابلیت اجرای لینوکس است.

- میکروکنترلر HiFive1 Rev B

- SparkFun RED-V RedBoard که یک میکروکنترلر در فرم Arduino است.

- LoFive RISC-V SoC evaluation kit

- ماژول امنیتی Titan M2 شرکت گوگل که برای گوشی موبایل Pixel 6 توسعه داده شده است.

علاوه بر اینها، معماری RISC-V در محصولات درحالتوسعه قابل توجهی استفاده میشود که ازجمله آنها میشود بهکارت گرافیکهای شرکت Nvidia اشاره کرد. این شرکت قصد دارد که پردازندههای Falcon خود را با RISC-V جایگزین کند.

یک مورد با اهمیت دیگر از پیادهسازی RISC-V شتابدهندهی هوش مصنوعی شرکت Esperanto با بیش از هزار هسته RISC-V است.

نتیجه

RISC-V از این نظر اهمیت زیادی دارد که سازندگان کوچکتر سختافزار را قادر میسازد بدون نیاز به پرداخت هزینهی معماری، دست به تولید بزنند. همچنین توسعهدهندگان و محققین میتوانند از یک معماری مجموعه دستورات رایگان و قدرتمند برای آزمایشها و طراحیهای خود استفاده کنند. علاوه بر همه اینها این موضوع سبب قوت گرفتن نوآوری و رقابت در دورهای شده است که تولیدکنندگان بزرگ، شرکتهای رقیب را خریداری میکنند. یک مصداق اخیر از این موضوع، تلاش Nvidia برای خریداری ARM بود، که البته با شکست مواجه شد. در آخر لازم به ذکر است که کامیونیتی RISC-V و منابع مهم این معماری از طریق صفحه رسمی RISC-V قابلدسترسی است.

منبع:سیسوگ